Inhaltsverzeichnis

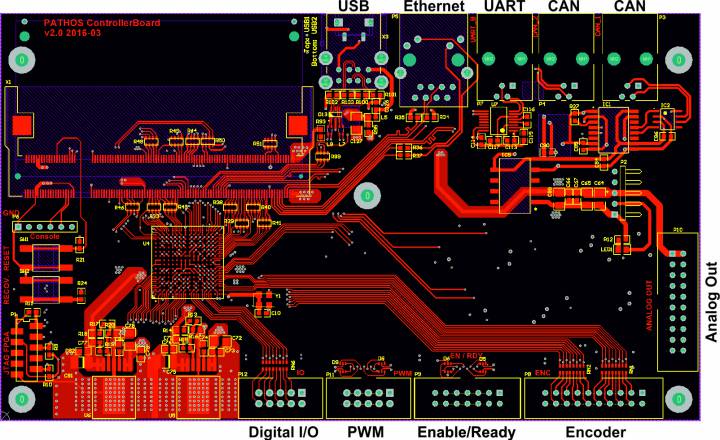

Controller Board with Colibri Module

cb11 Board

Features

- 1 x Ethernet

- 2 x CAN

- 24 DIO

- 8 Analog Out

- For Altium files together with FPGA designs see http://wiki.ntb.ch/projects/pathos/start

Important: For this board you have to load a different FPGA configuration as for the cb20.

Existing Boards

- 1 x cb11 Prototype (EMS) 2015

cb20 Board

Features

- 1 x Ethernet

- 2 x CAN

- 1 x USB Host

- 1 x Konsole, 1 x UART

- 24 DIO

- 8 Analog Out (+/-10V)

The board has a EP4CE22F17C8 FPGA from Altera which is connected over the EIM bus to the Colibri module.

- github repository with Altium files, FPGA designs, and test application https://gitlab.ost.ch/tech/inf/public/cb20

- Hardware configuration file for EEROS https://gitlab.ost.ch/tech/inf/public/cb20/blob/master/Software/cb20test/HwConfigCb20.json

The FPGA configuration for the cb20 is made with flink. The available blocks for flink can be found on flink-Wiki.

Existing Boards

- 8 x cb20 INF (Variosystems 2016) without CAN-GND

- 2 x cb20 EMS (Variosystems 2016) without CAN-GND

- 5 x cb22 INF different power plug (Anronaut 2017)

flink Configurations

Standard FPGA Design

The FPGA is driven by a 50MHz clock. The system incorporates a Avalon ALTPLL component which multiplies this clock with 4 leading to a internal clock of 200MHz. The flink blocks which depend on this clock must set their base clock setting accordingly. This configuration defines the following subdevices:

| flink component | unique id | id | nof channels | description |

|---|---|---|---|---|

| PWM | 0x1270C001 | 0 | 8 | |

| FQD | 0x12706001 | 1 | 8 | |

| Analog Out | 0x12702001 | 2 | 8 | |

| Info Device | 0x12700001 | 3 | cb20 standard, 28.5.2020 | |

| Dig I/O | 0x12705002 | 4 | 8 | |

| Dig I/O (Enable/Ready) | 0x12705001 | 5 | 9 |

The header and pin assignment are shown below. :

Test Program

There is a test program using EEROS under https://gitlab.ost.ch/tech/inf/public/cb20 for the above standard configuration. Use the steps described in https://wiki.eeros.org/getting_started/install/use_with_cb20 to fetch all necessary repositories and build the application. The application reads the suitable hardware configuration file HwConfigCb20.json and configures all pins. The analog and digital and PWM outputs are driven. The encoder inputs are periodically logged.

There is a second application cb11Test which uses HwConfigDb11.json. It only has 4 encoder inputs, together with analog ouputs, ready and enable signals. This test is used to check all the necessary functions for the later use of the cb20 with the drive board Drive Board der NTB.

FPGA Design with Watchdog and PPWA

| flink component | unique id | id | nof channels | description |

|---|---|---|---|---|

| PWM | 0x1270C001 | 0 | 4 | |

| PPWA | 0x12706001 | 1 | 2 | |

| Watchdog | 0x12710001 | 2 | 1 | |

| FQD | 0x12706001 | 3 | 8 | |

| Analog Out | 0x12702001 | 4 | 8 | |

| Info Device | 0x12700001 | 5 | cb20 with wdt, 28.5.2020 | |

| Dig I/O | 0x12705002 | 6 | 8 | |

| Dig I/O (Enable/Ready) | 0x12705001 | 7 | 9 |

The pins are assigned as with the standard configuration with the following exceptions: P11 has 4 PWM channels (pin 1 to 4), PPWA is on pin 5 and 6, Watchdog is on pin 7 (granted) and 8 (pwm).

FPGA Design with MPU9250

This design incorporates a SPI connection to a MPU9250 sensor. The SPI occupies 4 pins on the PWM connector.

| flink component | unique id | id | nof channels | description |

|---|---|---|---|---|

| PWM | 0x1270C001 | 0 | 4 | |

| MPU9250 | 0x12711001 | 1 | ||

| FQD | 0x12706001 | 2 | 8 | |

| Analog Out | 0x12702001 | 3 | 8 | |

| Info Device | 0x12700001 | 4 | ||

| Dig I/O | 0x12705002 | 5 | 8 | |

| Dig I/O (Enable/Ready) | 0x12705001 | 6 | 9 |

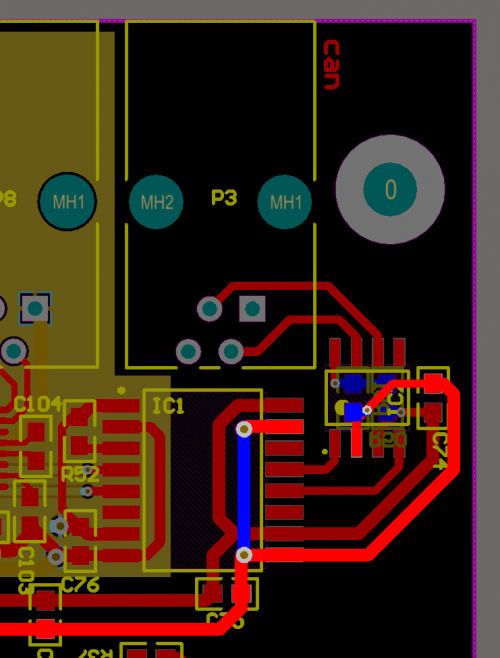

Known Errors

If CAN is used to connect to a drive with high power, CAN GND must be connected. This connection is missing on the board version 11 and 20. You have to connect GND_ISO with pin4 of the CAN connector. The highlighted lines are GND_ISO and CAN GND.