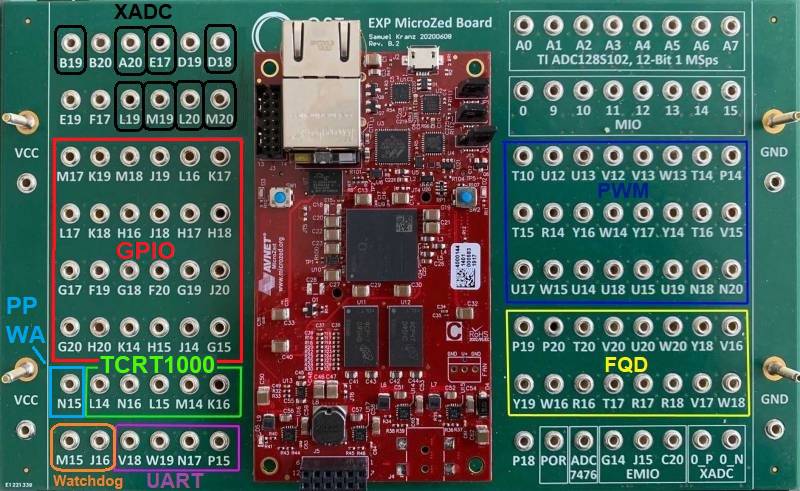

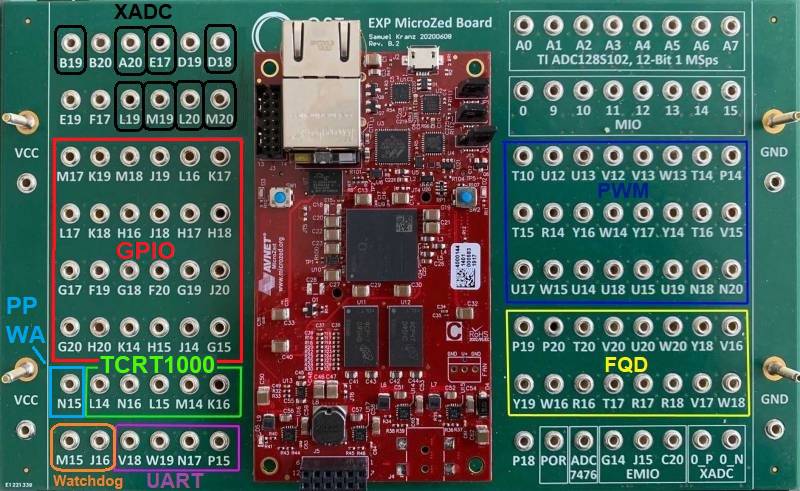

Pin Mapping for flink2 Configuration

| FPGA Pin | Flink Device | Flink Channel |

| M17 | GPIO | 0 |

| K19 | 1 |

| M18 | 2 |

| J19 | 3 |

| L16 | 4 |

| K17 | 5 |

| L17 | 6 |

| K18 | 7 |

| H16 | 8 |

| J18 | 9 |

| H17 | 10 |

| H18 | 11 |

| G17 | 12 |

| F19 | 13 |

| G18 | 14 |

| F20 | 15 |

| G19 | 16 |

| J20 | 17 |

| G20 | 18 |

| H20 | 19 |

| K14 | 20 |

| H15 | 21 |

| J14 | 22 |

| G15 | 23 |

| FPGA Pin | Flink Device | Flink Channel |

| N15 | PPWA | 0 |

| FPGA Pin | Flink Device | Function |

| L14 | TCRT1000 | Trig |

| N16 | Address 0 |

| L15 | Address 1 |

| M14 | Address 2 |

| K16 | Address 3 |

| FPGA Pin | Flink Device | Flink Channel |

| T10 | PWM | 0 |

| U12 | 1 |

| U13 | 2 |

| V12 | 3 |

| V13 | 4 |

| W13 | 5 |

| T14 | 6 |

| P14 | 7 |

| T15 | 8 |

| R14 | 9 |

| Y16 | 10 |

| W14 | 11 |

| Y17 | 12 |

| Y14 | 13 |

| T16 | 14 |

| V15 | 15 |

| U17 | 16 |

| W15 | 17 |

| U14 | 18 |

| U18 | 19 |

| U15 | 20 |

| U19 | 21 |

| N18 | 22 |

| N20 | 23 |

| FPGA Pin | Flink Device | Flink Channel |

| V18 | UART | TX[0] |

| W19 | RX[0] |

| N17 | TX[1] |

| P15 | RX[1] |

| FPGA Pin | Flink Device | Function |

| M15 | Watchdog | PWM |

| J16 | Watchdog | Granted |

| FPGA Pin | Flink Device | Flink Channel |

| P19 | FQD | 0[A] |

| P20 | 0[B] |

| T20 | 1[A] |

| V20 | 1[B] |

| U20 | 2[A] |

| W20 | 2[B] |

| Y18 | 3[A] |

| V16 | 3[B] |

| Y19 | 4[A] |

| W16 | 4[B] |

| R16 | 5[A] |

| T17 | 5[B] |

| R17 | 6[A] |

| R18 | 6[B] |

| V17 | 7[A] |

| W18 | 7[B] |

| FPGA Pin | Flink Device | ADC Pin |

| T11 | ADC128S102 | DIN |

| T19 | SCLK |

| R19 | CSN |

| T12 | DOUT |

| FPGA Pin | Flink Device | ADC Pin |

| D20 | AD7476 | SCLK |

| F16 | CSN |

| E18 | DATA |

| FPGA Pin | XADC Device | Channel |

| E17 | XADC | 0[p] |

| D18 | 0[n] |

| M19 | 1[p] |

| M20 | 1[n] |

| L19 | 2[p] |

| L20 | 2[n] |

| B19 | 3[p] |

| A20 | 3[n] |