## TMS320C67x/C67x+ DSP CPU and Instruction Set Reference Guide

Literature Number: SPRU733A November 2006

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated

#### Preface

## **Read This First**

#### About This Manual

The TMS320C6000<sup>™</sup> digital signal processor (DSP) platform is part of the TMS320<sup>™</sup> DSP family. The TMS320C62x<sup>™</sup> DSP generation and the TMS320C64x<sup>™</sup> DSP generation comprise fixed-point devices in the C6000<sup>™</sup> DSP platform, and the TMS320C67x<sup>™</sup> DSP generation comprises floating-point devices in the C6000 DSP platform.

The TMS320C67x+<sup>TM</sup> DSP is an enhancement of the C67x<sup>TM</sup> DSP with added functionality and an expanded instruction set. This document describes the CPU architecture, pipeline, instruction set, and interrupts of the C67x and C67x+<sup>TM</sup> DSPs.

#### Notational Conventions

This document uses the following conventions.

- □ Any reference to the C67x DSP or C67x CPU also applies, unless otherwise noted, to the C67x+ DSP and C67x+ CPU, respectively.

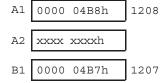

- □ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### **Related Documentation From Texas Instruments**

The following documents describe the C6000<sup>TM</sup> devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the C6000 devices, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: www.ti.com/c6000.

*TMS320C6000 DSP Peripherals Overview Reference Guide* (literature number SPRU190) describes the peripherals available on the TMS320C6000 DSPs.

- *TMS320C672x DSP Peripherals Overview Reference Guide* (literature number SPRU723) describes the peripherals available on the TMS320C672x DSPs.

- **TMS320C6000 Technical Brief** (literature number SPRU197) gives an introduction to the TMS320C62x and TMS320C67x DSPs, development tools, and third-party support.

- **TMS320C6000 Programmer's Guide** (literature number SPRU198) describes ways to optimize C and assembly code for the TMS320C6000 DSPs and includes application program examples.

- *TMS320C6000 Code Composer Studio Tutorial* (literature number SPRU301) introduces the Code Composer Studio integrated development environment and software tools.

- **Code Composer Studio Application Programming Interface Reference Guide** (literature number SPRU321) describes the Code Composer Studio application programming interface (API), which allows you to program custom plug-ins for Code Composer.

- **TMS320C6x Peripheral Support Library Programmer's Reference** (literature number SPRU273) describes the contents of the TMS320C6000 peripheral support library of functions and macros. It lists functions and macros both by header file and alphabetically, provides a complete description of each, and gives code examples to show how they are used.

- **TMS320C6000** Chip Support Library API Reference Guide (literature number SPRU401) describes a set of application programming interfaces (APIs) used to configure and control the on-chip peripherals.

#### Trademarks

Code Composer Studio, C6000, C64x, C67x, C67x+, TMS320C2000, TMS320C5000, TMS320C6000, TMS320C62x, TMS320C64x, TMS320C67x, TMS320C67x+, TMS320C672x, and VelociTI are trademarks of Texas Instruments.

Trademarks are the property of their respective owners.

# Contents

| 1 | Sumn                                          | narizes t                                                                                                                    | he features of the TMS320 family of products and presents typical applications                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |

|---|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|   | Desci<br>1.1<br>1.2<br>1.3<br>1.4             | TMS32<br>TMS32<br>TMS32                                                                                                      | TMS320C67x DSP and lists their key features.         0 DSP Family Overview         0C6000 DSP Family Overview         0C67x DSP Features and Options         0C67x DSP Architecture         Central Processing Unit (CPU)         Internal Memory         Memory and Peripheral Options                                                                                                                                                                              | 1-2<br>1-4<br>1-7<br>1-8<br>1-8                                               |

| 2 | Provie                                        | des infor                                                                                                                    | ths and Control<br>mation about the data paths and control registers. The two register files and the<br>ths are described.                                                                                                                                                                                                                                                                                                                                           |                                                                               |

|   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Introdu<br>Genera<br>Functio<br>Registe<br>Memor<br>Data Au<br>Control<br>2.7.1<br>2.7.2<br>2.7.3<br>2.7.4<br>2.7.5<br>2.7.6 | ction .<br>II-Purpose Register Files                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-2<br>2-5<br>2-6<br>2-7<br>2-7<br>2-8<br>2-9<br>2-10<br>2-13<br>2-16<br>2-17 |

|   | 2.8                                           |                                                                                                                              | Interrupt Flag Register (IFR)<br>Interrupt Return Pointer Register (IRP)<br>Interrupt Set Register (ISR)<br>Interrupt Service Table Pointer Register (ISTP)<br>Nonmaskable Interrupt (NMI) Return Pointer Register (NRP)<br>E1 Phase Program Counter (PCE1)<br>Register File Extensions<br>Floating-Point Adder Configuration Register (FADCR)<br>Floating-Point Auxiliary Configuration Register (FAUCR)<br>Floating-Point Multiplier Configuration Register (FMCR) | 2-19<br>2-20<br>2-21<br>2-22<br>2-22<br>2-23<br>2-23<br>2-23<br>2-27          |

Contents

V

| 3 | Desci | ribes the | Set<br>e assembly language instructions of the TMS320C67x DSP. Also desc<br>ations, conditional operations, resource constraints, and addressing mo | ribed are |

|---|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 3.1   |           | xtion Operation and Execution Notations                                                                                                             |           |

|   | 3.2   |           | tion Syntax and Opcode Notations                                                                                                                    |           |

|   | 3.3   |           | ew of IEEE Standard Single- and Double-Precision Formats                                                                                            |           |

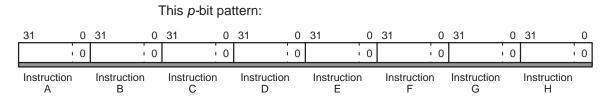

|   | 3.4   |           | Slots                                                                                                                                               |           |

|   | 3.5   |           | el Operations                                                                                                                                       |           |

|   | 5.5   | 3.5.1     | Example Parallel Code                                                                                                                               |           |

|   |       | 3.5.2     | Branching Into the Middle of an Execute Packet                                                                                                      |           |

|   | 3.6   |           | ional Operations                                                                                                                                    |           |

|   | 3.7   |           | rce Constraints                                                                                                                                     |           |

|   | 5.7   | 3.7.1     | Constraints on Instructions Using the Same Functional Unit                                                                                          |           |

|   |       | 3.7.2     | Constraints on the Same Functional Unit Writing in the<br>Same Instruction Cycle                                                                    |           |

|   |       | 3.7.3     | Constraints on Cross Paths (1X and 2X)                                                                                                              |           |

|   |       | 3.7.4     | Constraints on Loads and Stores                                                                                                                     |           |

|   |       | 3.7.5     | Constraints on Long (40-Bit) Data                                                                                                                   |           |

|   |       | 3.7.6     | Constraints on Register Reads                                                                                                                       |           |

|   |       | 3.7.7     | Constraints on Register Writes                                                                                                                      |           |

|   |       | 3.7.8     | Constraints on Floating-Point Instructions                                                                                                          |           |

|   | 3.8   |           | ssing Modes                                                                                                                                         |           |

|   |       | 3.8.1     | Linear Addressing Mode                                                                                                                              |           |

|   |       | 3.8.2     | Circular Addressing Mode                                                                                                                            |           |

|   |       | 3.8.3     | Syntax for Load/Store Address Generation                                                                                                            |           |

|   | 3.9   | Instruc   | tion Compatibility                                                                                                                                  |           |

|   | 3.10  |           | tion Descriptions                                                                                                                                   |           |

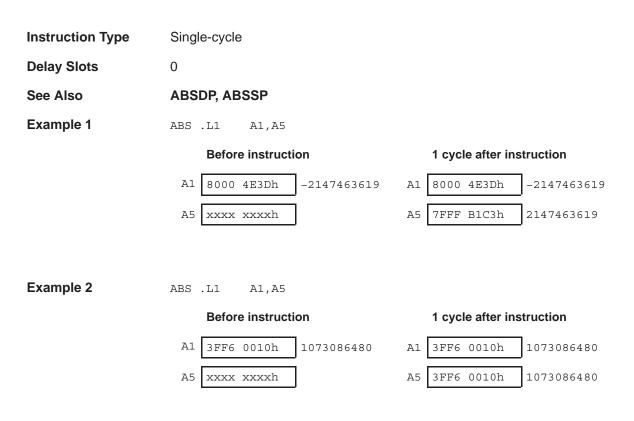

|   |       |           | Absolute Value With Saturation)                                                                                                                     |           |

|   |       | •         | P (Absolute Value, Double-Precision Floating-Point)                                                                                                 |           |

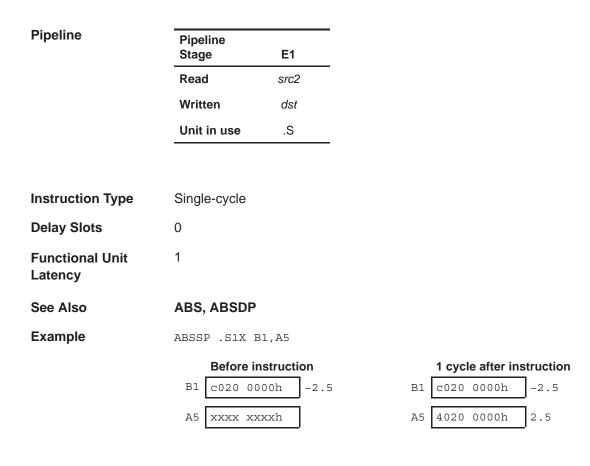

|   |       |           | P (Absolute Value, Single-Precision Floating-Point)                                                                                                 |           |

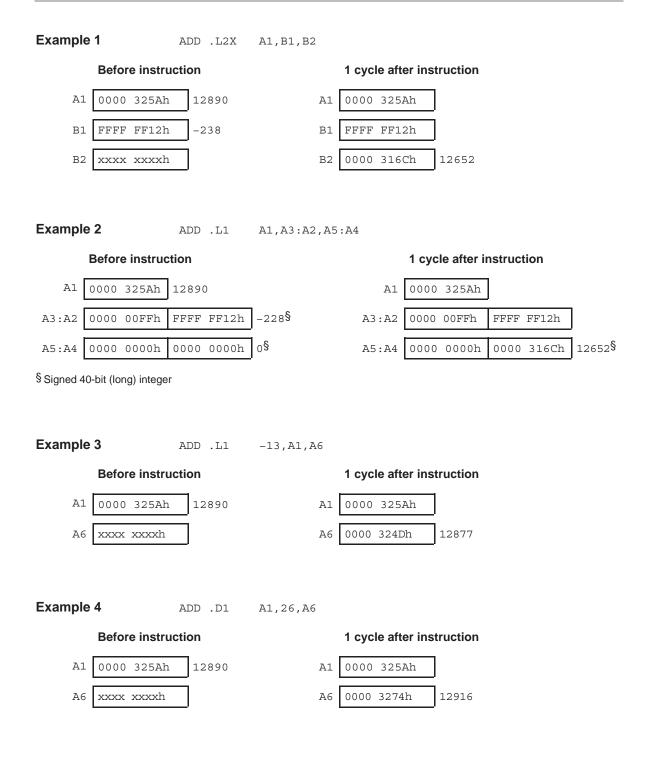

|   |       | ADD (/    | Add Two Signed Integers Without Saturation)                                                                                                         | 3-43      |

|   |       | ADDA      | B (Add Using Byte Addressing Mode)                                                                                                                  | 3-47      |

|   |       | ADDA      | D (Add Using Doubleword Addressing Mode)                                                                                                            | 3-49      |

|   |       | ADDA      | H (Add Using Halfword Addressing Mode)                                                                                                              | 3-51      |

|   |       | ADDA      | W (Add Using Word Addressing Mode)                                                                                                                  | 3-53      |

|   |       | ADDD      | P (Add Two Double-Precision Floating-Point Values)                                                                                                  | 3-55      |

|   |       | ADDK      | (Add Signed 16-Bit Constant to Register)                                                                                                            | 3-58      |

|   |       | ADDS      | P (Add Two Single-Precision Floating-Point Values)                                                                                                  | 3-59      |

|   |       | ADDU      | (Add Two Unsigned Integers Without Saturation)                                                                                                      | 3-62      |

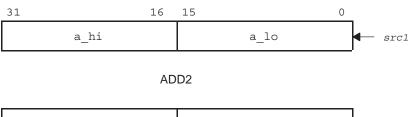

|   |       | ADD2      | (Add Two 16-Bit Integers on Upper and Lower Register Halves)                                                                                        | 3-64      |

|   |       |           | Bitwise AND)                                                                                                                                        |           |

|   |       | B (Bra    | nch Using a Displacement)                                                                                                                           | 3-68      |

|   |       |           | nch Using a Register)                                                                                                                               |           |

|   |       |           | (Branch Using an Interrupt Return Pointer)                                                                                                          |           |

|   |       | B NRF     | P (Branch Using NMI Return Pointer)                                                                                                                 | 3-74      |

Contents

| CLR (Clear a Bit Field)                                                                   | . 3-76 |

|-------------------------------------------------------------------------------------------|--------|

| CMPEQ (Compare for Equality, Signed Integers)                                             |        |

| CMPEQDP (Compare for Equality, Double-Precision Floating-Point Values)                    |        |

| CMPEQSP (Compare for Equality, Single-Precision Floating-Point Values)                    |        |

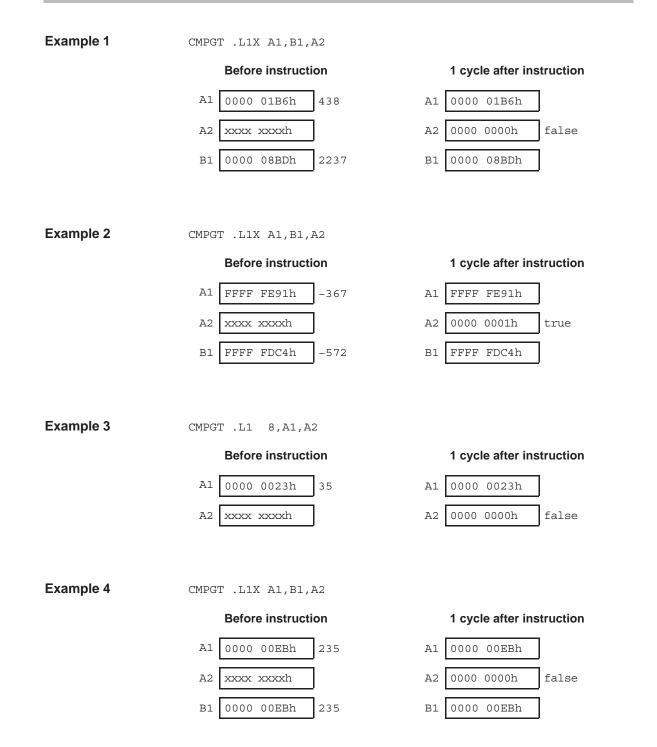

| CMPGT (Compare for Greater Than, Signed Integers)                                         |        |

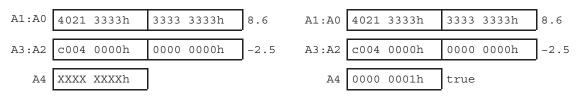

| CMPGTDP (Compare for Greater Than, Double-Precision Floating-Point Values) .              |        |

| CMPGTSP (Compare for Greater Than, Single-Precision Floating-Point Values)                |        |

| CMPGTU (Compare for Greater Than, Unsigned Integers)                                      |        |

| CMPLT (Compare for Less Than, Signed Integers)                                            |        |

| CMPLTDP (Compare for Less Than, Double-Precision Floating-Point Values)                   |        |

| CMPLTSP (Compare for Less Than, Single-Precision Floating-Point Values)                   |        |

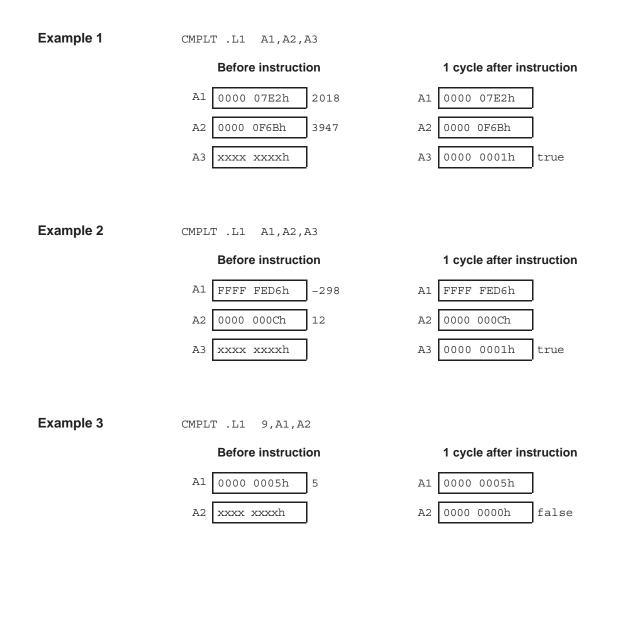

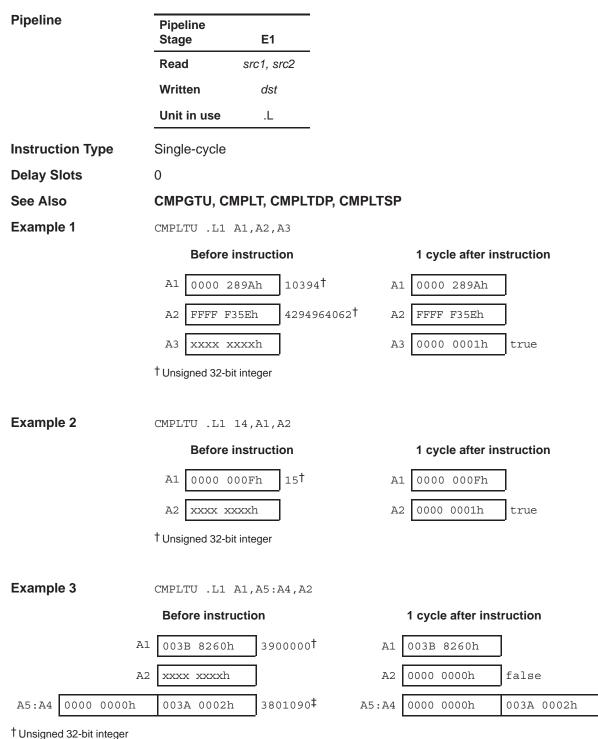

| CMPLTU (Compare for Less Than, Unsigned Integers)                                         |        |

| DPINT (Convert Double-Precision Floating-Point Value to Integer)                          |        |

| DPSP (Convert Double-Precision Floating-Point Value to                                    |        |

| Single-Precision Floating-Point Value)                                                    | 3-105  |

| DPTRUNC (Convert Double-Precision Floating-Point Value to                                 |        |

| Integer With Truncation)                                                                  |        |

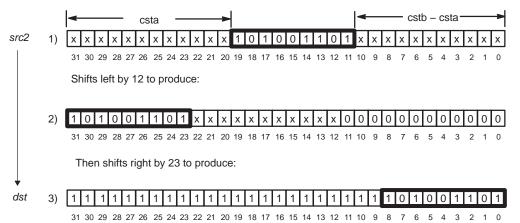

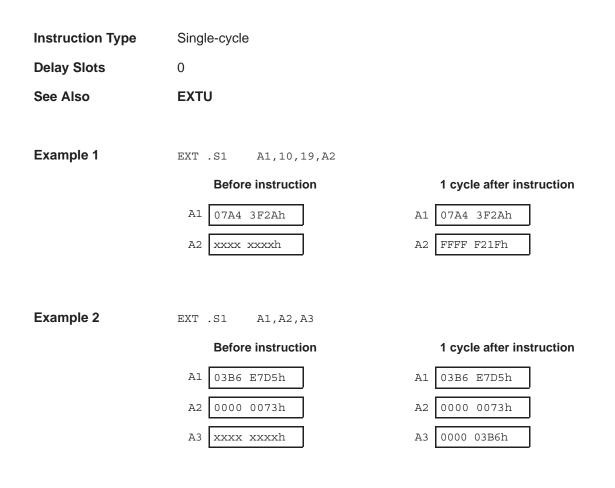

| EXT (Extract and Sign-Extend a Bit Field)                                                 |        |

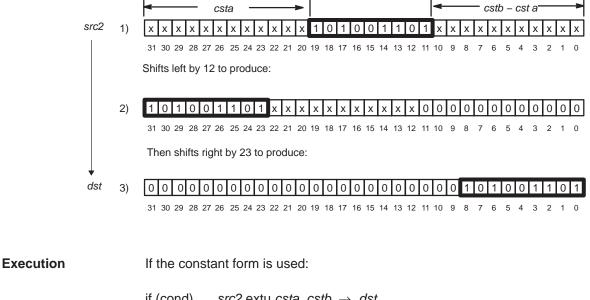

| EXTU (Extract and Zero-Extend a Bit Field)                                                |        |

| IDLE (Multicycle NOP With No Termination Until Interrupt)                                 |        |

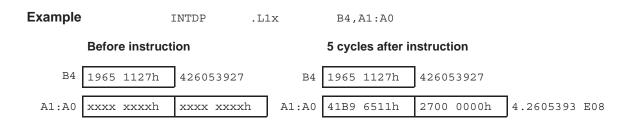

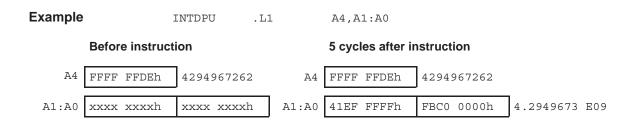

| INTDP (Convert Signed Integer to Double-Precision Floating-Point Value)                   | 3-116  |

| INTDPU (Convert Unsigned Integer to Double-Precision Floating-Point Value)                | 3-118  |

| INTSP (Convert Signed Integer to Single-Precision Floating-Point Value)                   | 3-120  |

| INTSPU (Convert Unsigned Integer to Single-Precision Floating-Point Value)                | 3-121  |

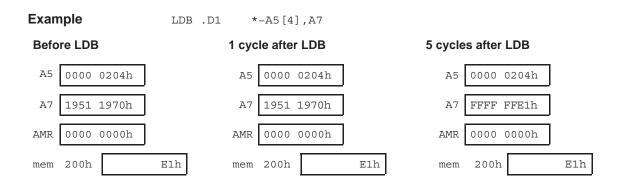

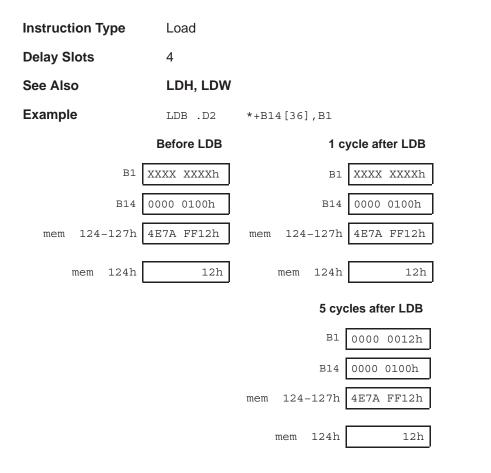

| LDB(U) (Load Byte From Memory With a 5-Bit Unsigned Constant Offset                       | 0.400  |

| or Register Offset)                                                                       |        |

| LDB(U) (Load Byte From Memory With a 15-Bit Unsigned Constant Offset)                     | 3-125  |

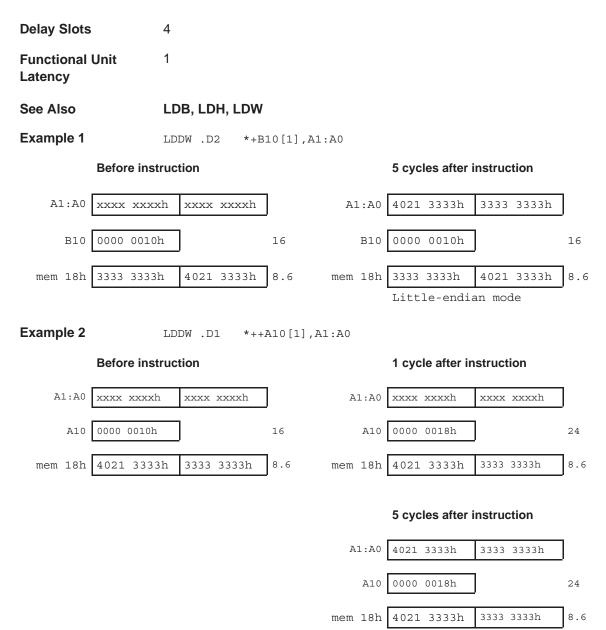

| LDDW (Load Doubleword From Memory With an Unsigned Constant Offset<br>or Register Offset) | 3-127  |

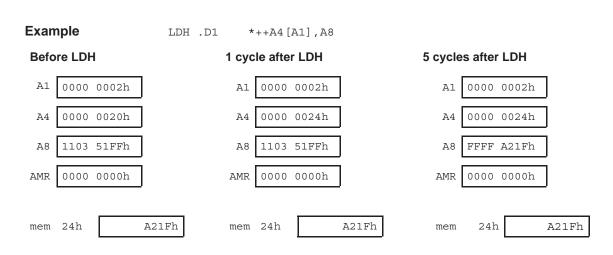

| LDH(U) (Load Halfword From Memory With a 5-Bit Unsigned Constant Offset                   | 0 121  |

| or Register Offset)                                                                       | 3-130  |

| LDH(U) (Load Halfword From Memory With a 15-Bit Unsigned Constant Offset)                 | 3-133  |

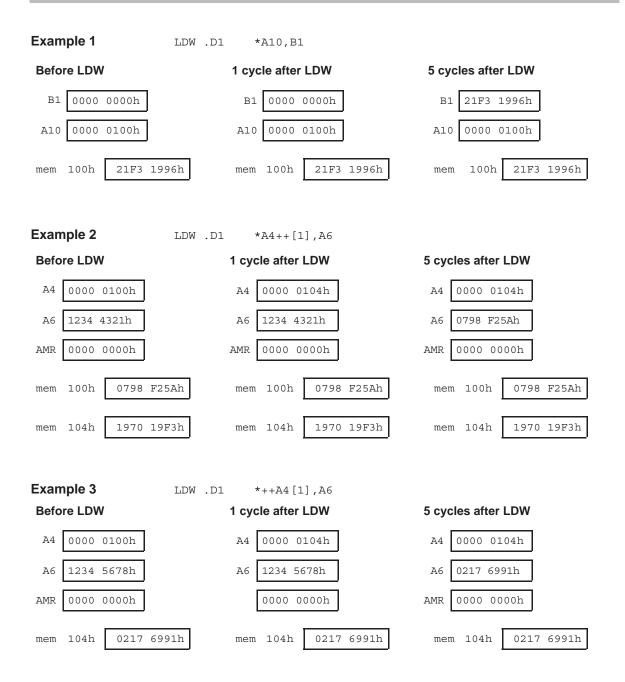

| LDW (Load Word From Memory With a 5-Bit Unsigned Constant Offset                          |        |

| or Register Offset)                                                                       | 3-135  |

| LDW (Load Word From Memory With a 15-Bit Unsigned Constant Offset)                        | 3-138  |

| LMBD (Leftmost Bit Detection)                                                             |        |

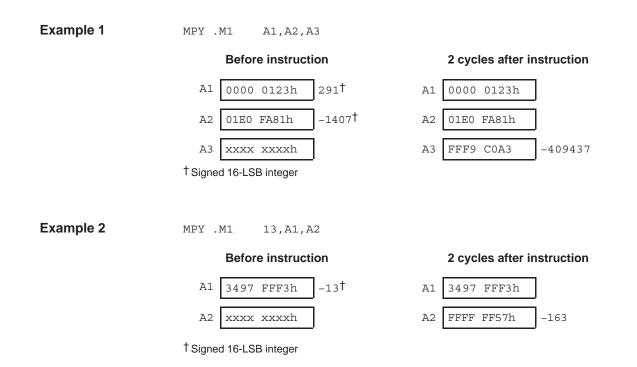

| MPY (Multiply Signed 16 LSB by Signed 16 LSB)                                             |        |

| MPYDP (Multiply Two Double-Precision Floating-Point Values)                               |        |

| MPYH (Multiply Signed 16 MSB by Signed 16 MSB)                                            |        |

| MPYHL (Multiply Signed 16 MSB by Signed 16 LSB)                                           |        |

| MPYHLU (Multiply Unsigned 16 MSB by Unsigned 16 LSB)                                      |        |

| MPYHSLU (Multiply Signed 16 MSB by Unsigned 16 LSB)                                       | 3-151  |

| MPYHSU (Multiply Signed 16 MSB by Unsigned 16 MSB)                                        |        |

| MPYHU (Multiply Unsigned 16 MSB by Unsigned 16 MSB)                                       |        |

| MPYHULS (Multiply Unsigned 16 MSB by Signed 16 LSB)                                       |        |

| MPYHUS (Multiply Unsigned 16 MSB by Signed 16 MSB)                                        | 3-155  |

vii

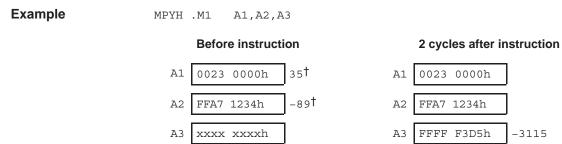

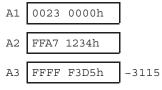

| MPYI (Multiply 32-Bit by 32-Bit Into 32-Bit Result)               | 3-156 |

|-------------------------------------------------------------------|-------|

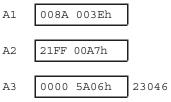

| MPYID (Multiply 32-Bit by 32-Bit Into 64-Bit Result)              | 3-158 |

| MPYLH (Multiply Signed 16 LSB by Signed 16 MSB)                   |       |

| MPYLHU (Multiply Unsigned 16 LSB by Unsigned 16 MSB)              |       |

| MPYLSHU (Multiply Signed 16 LSB by Unsigned 16 MSB)               |       |

| MPYLUHS (Multiply Unsigned 16 LSB by Signed 16 MSB)               |       |

| MPYSP (Multiply Two Single-Precision Floating-Point Values)       |       |

| MPYSPDP (Multiply Single-Precision Floating-Point Value by        | 0 100 |

| Double-Precision Floating-Point Value)                            | 3-167 |

| MPYSP2DP (Multiply Two Single-Precision Floating-Point Values     | 0.01  |

| for Double-Precision Result)                                      | 3-169 |

| MPYSU (Multiply Signed 16 LSB by Unsigned 16 LSB)                 | 3-171 |

| MPYU (Multiply Unsigned 16 LSB by Unsigned 16 LSB)                |       |

| MPYUS (Multiply Unsigned 16 LSB by Signed 16 LSB)                 |       |

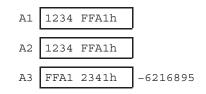

| MV (Move From Register to Register)                               |       |

| MVC (Move Between Control File and Register File)                 |       |

| MVK (Move Signed Constant Into Register and Sign Extend)          |       |

| MVKH and MVKLH (Move 16-Bit Constant Into Upper Bits of Register) |       |

| MVKL (Move Signed Constant Into Register and                      | 0 101 |

| Sign Extend—Used with MVKH)                                       | 3-186 |

| NEG (Negate)                                                      |       |

| NOP (No Operation)                                                |       |

| NORM (Normalize Integer)                                          |       |

| NOT (Bitwise NOT)                                                 |       |

| OR (Bitwise OR)                                                   |       |

| RCPDP (Double-Precision Floating-Point Reciprocal Approximation)  |       |

|                                                                   | 3-198 |

| RSQRDP (Double-Precision Floating-Point Square-Root Reciprocal    | 5-190 |

| Approximation)                                                    | 3-200 |

| RSQRSP (Single-Precision Floating-Point Square-Root Reciprocal    | 0 200 |

| Approximation)                                                    | 3-202 |

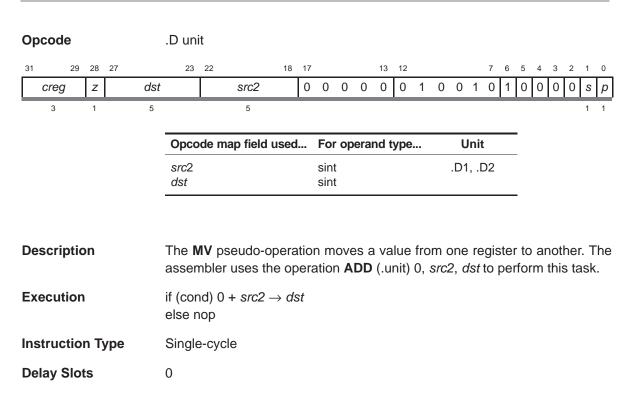

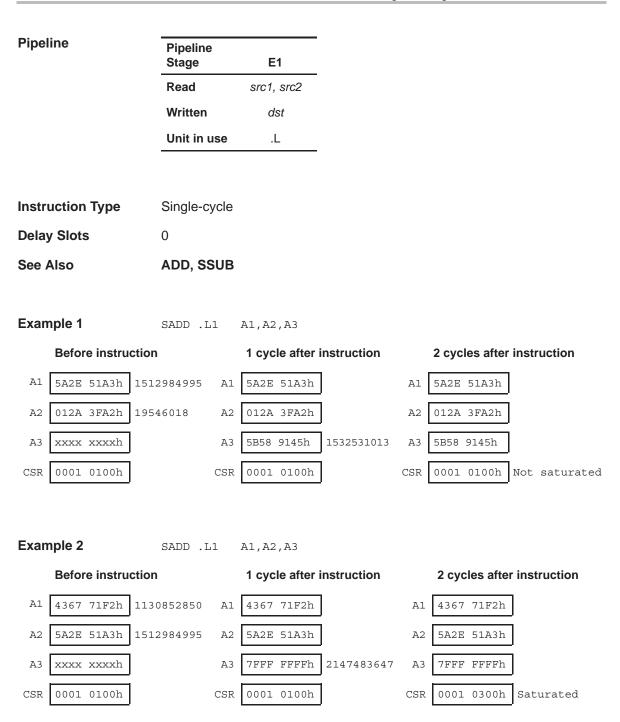

| SADD (Add Two Signed Integers With Saturation)                    |       |

| SAT (Saturate a 40-Bit Integer to a 32-Bit Integer)               |       |

| SET (Set a Bit Field)                                             |       |

| SHL (Arithmetic Shift Left)                                       |       |

| SHR (Arithmetic Shift Right)                                      |       |

| SHRU (Logical Shift Right)                                        |       |

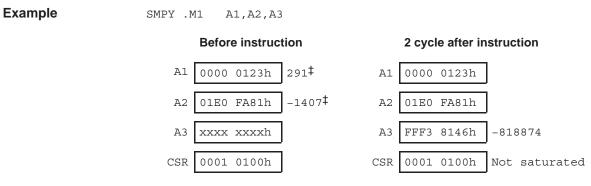

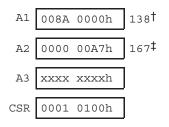

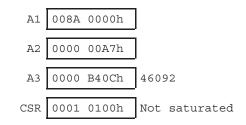

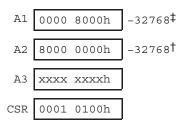

| SMPY (Multiply Signed 16 LSB by Signed 16 LSB                     | 0 210 |

| With Left Shift and Saturation)                                   | 3-218 |

| SMPYH (Multiply Signed 16 MSB by Signed 16 MSB                    |       |

| With Left Shift and Saturation)                                   | 3-220 |

| SMPYHL (Multiply Signed 16 MSB by Signed 16 LSB                   |       |

| With Left Shift and Saturation)                                   | 3-221 |

| SMPYLH (Multiply Signed 16 LSB by Signed 16 MSB                   |       |

| With Left Shift and Saturation)                                   | 3-223 |

| SPDP (Convert Single-Precision Floating-Point Value to            | 2 225 |

| Double-Precision Floating-Point Value)                            | 3-225 |

|                                                                   |       |

Contents

SPRU733A

|        | SPINT                                                                                                                                  | (Convert Single-Precision Floating-Point Value to Integer)                                                                                                                                                                                                                                                                                                        | 3-227                                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|        | SPTRL                                                                                                                                  | INC (Convert Single-Precision Floating-Point Value to                                                                                                                                                                                                                                                                                                             |                                                                                                                          |

|        |                                                                                                                                        | Integer With Truncation)                                                                                                                                                                                                                                                                                                                                          |                                                                                                                          |

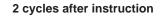

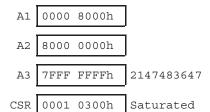

|        |                                                                                                                                        | Shift Left With Saturation)                                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

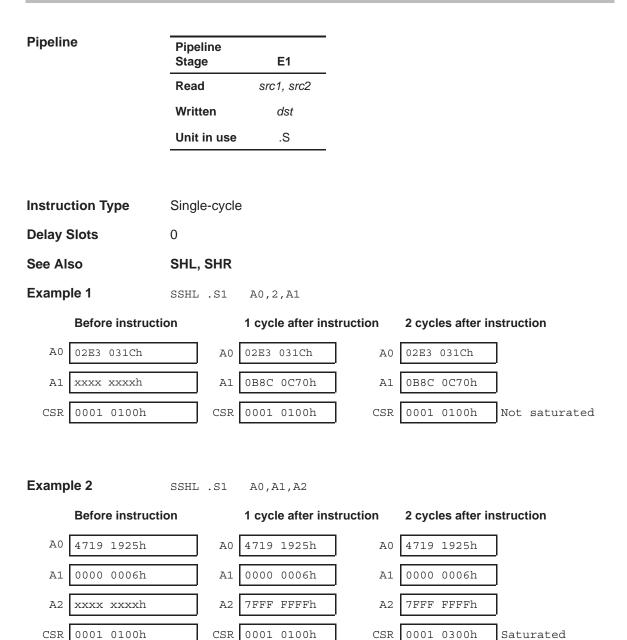

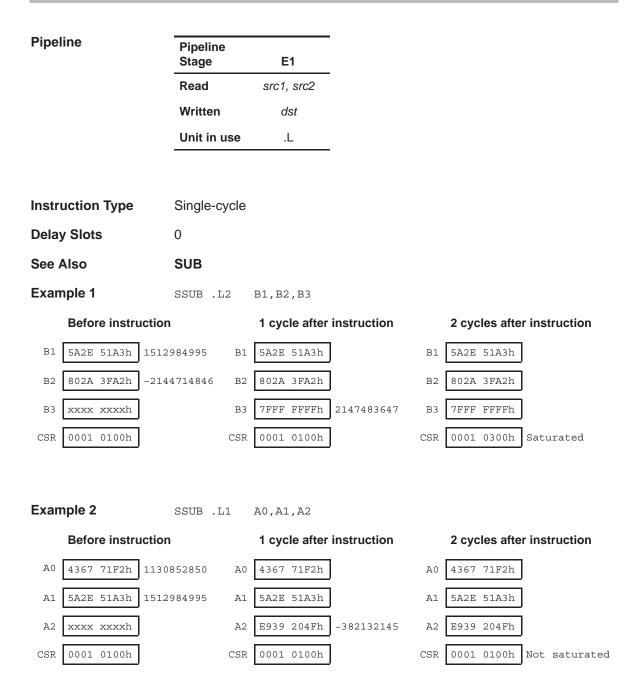

|        |                                                                                                                                        | (Subtract Two Signed Integers With Saturation)                                                                                                                                                                                                                                                                                                                    | 3-233                                                                                                                    |

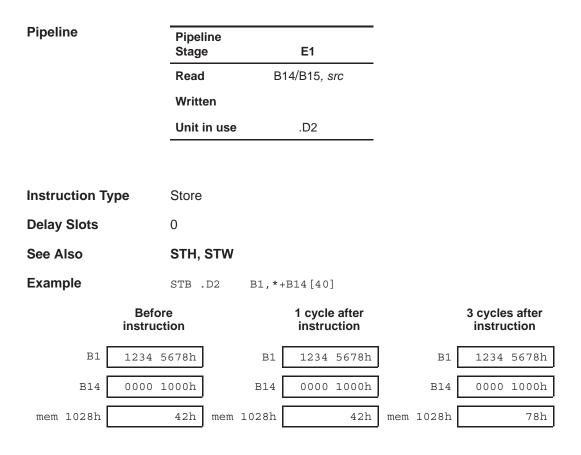

|        | SIB (S                                                                                                                                 | tore Byte to Memory With a 5-Bit Unsigned Constant Offset<br>or Register Offset)                                                                                                                                                                                                                                                                                  | 3-235                                                                                                                    |

|        | STB (S                                                                                                                                 | tore Byte to Memory With a 15-Bit Unsigned Constant Offset)                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

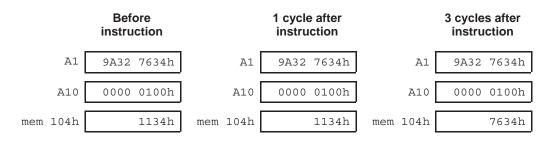

|        |                                                                                                                                        | store Halfword to Memory With a 5-Bit Unsigned Constant Offset                                                                                                                                                                                                                                                                                                    | 0 201                                                                                                                    |

|        |                                                                                                                                        | or Register Offset)                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

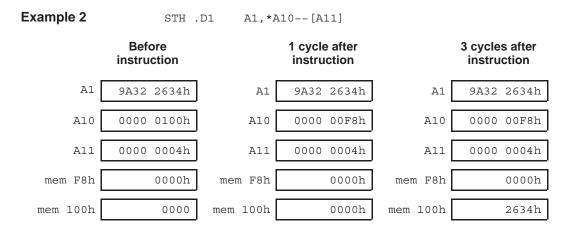

|        | •                                                                                                                                      | tore Halfword to Memory With a 15-Bit Unsigned Constant Offset)                                                                                                                                                                                                                                                                                                   | 3-242                                                                                                                    |

|        | STW (S                                                                                                                                 | Store Word to Memory With a 5-Bit Unsigned Constant Offset                                                                                                                                                                                                                                                                                                        | 2 244                                                                                                                    |

|        | ST/1/ (                                                                                                                                | or Register Offset)                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

|        | •                                                                                                                                      | Store Word to Memory With a 15-Bit Unsigned Constant Offset)                                                                                                                                                                                                                                                                                                      |                                                                                                                          |

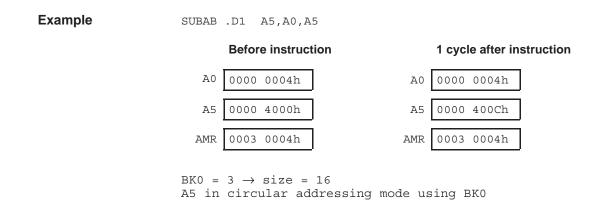

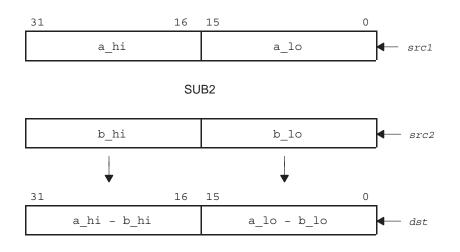

|        | •                                                                                                                                      | Subtract Two Signed Integers Without Saturation)                                                                                                                                                                                                                                                                                                                  |                                                                                                                          |

|        |                                                                                                                                        | Subtract Using Byte Addressing Mode)     Subtract Using Holfword Addressing Mode)                                                                                                                                                                                                                                                                                 |                                                                                                                          |

|        |                                                                                                                                        | I (Subtract Using Halfword Addressing Mode)                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

|        |                                                                                                                                        | V (Subtract Using Word Addressing Mode)                                                                                                                                                                                                                                                                                                                           |                                                                                                                          |

|        |                                                                                                                                        | (Subtract Conditionally and Shift—Used for Division)                                                                                                                                                                                                                                                                                                              |                                                                                                                          |

|        |                                                                                                                                        | P (Subtract Two Double-Precision Floating-Point Values)                                                                                                                                                                                                                                                                                                           |                                                                                                                          |

|        |                                                                                                                                        | O (Subtract Two Single-Precision Floating-Point Values)           (Subtract Two Lipsigned Integers Without Seturation)                                                                                                                                                                                                                                            |                                                                                                                          |

|        |                                                                                                                                        | (Subtract Two Unsigned Integers Without Saturation)                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

|        | ,                                                                                                                                      | <b>o</b> 11 <b>o</b> ,                                                                                                                                                                                                                                                                                                                                            |                                                                                                                          |

|        | •                                                                                                                                      | Bitwise Exclusive OR)                                                                                                                                                                                                                                                                                                                                             |                                                                                                                          |

|        | ZERU                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                   | 3-271                                                                                                                    |

| Pipeli | ne                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                   | 4-1                                                                                                                      |

| Descr  | ibes pha                                                                                                                               | ases, operation, and discontinuities for the TMS320C67x CPU pipeline.                                                                                                                                                                                                                                                                                             |                                                                                                                          |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                          |

| 4.1    | Pipelin                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                   | 4-2                                                                                                                      |

| 4.1    | Pipeline<br>4.1.1                                                                                                                      | e Operation Overview                                                                                                                                                                                                                                                                                                                                              |                                                                                                                          |

| 4.1    | •                                                                                                                                      | e Operation Overview                                                                                                                                                                                                                                                                                                                                              | 4-2                                                                                                                      |

| 4.1    | 4.1.1                                                                                                                                  | e Operation Overview<br>Fetch<br>Decode                                                                                                                                                                                                                                                                                                                           | 4-2<br>4-3                                                                                                               |

| 4.1    | 4.1.1<br>4.1.2                                                                                                                         | e Operation Overview<br>Fetch<br>Decode<br>Execute                                                                                                                                                                                                                                                                                                                | 4-2<br>4-3<br>4-5                                                                                                        |

| 4.1    | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                                                                       | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary                                                                                                                                                                                                                                                                                  | 4-2<br>4-3<br>4-5<br>4-6                                                                                                 |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                                                                       | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types                                                                                                                                                                                                                                              | 4-2<br>4-3<br>4-5<br>4-6<br>4-12                                                                                         |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline                                                                                           | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions                                                                                                                                                                                                                 | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16                                                                                 |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline<br>4.2.1                                                                                  | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions<br>$16 \times 16$ -Bit Multiply Instructions                                                                                                                                                                    | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-17                                                                         |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline<br>4.2.1<br>4.2.2                                                                         | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions                                                                                                                                                                                                                 | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-17<br>4-18                                                                 |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline<br>4.2.1<br>4.2.2<br>4.2.3                                                                | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions<br>16 × 16-Bit Multiply Instructions<br>Store Instructions                                                                                                                                                      | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-17<br>4-18<br>4-20                                                         |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                                       | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions<br>$16 \times 16$ -Bit Multiply Instructions<br>Store Instructions<br>Load Instructions<br>Branch Instructions                                                                                                  | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-17<br>4-18<br>4-20<br>4-22                                                 |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                              | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions<br>$16 \times 16$ -Bit Multiply Instructions<br>Store Instructions<br>Load Instructions<br>Two-Cycle DP Instructions                                                                                            | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-16<br>4-17<br>4-18<br>4-20<br>4-22<br>4-24                                 |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6                                     | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions<br>$16 \times 16$ -Bit Multiply Instructions<br>Store Instructions<br>Load Instructions<br>Branch Instructions                                                                                                  | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-16<br>4-17<br>4-18<br>4-20<br>4-22<br>4-24<br>4-25                         |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipelind<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7                            | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions<br>$16 \times 16$ -Bit Multiply Instructions<br>Store Instructions<br>Load Instructions<br>Branch Instructions<br>Two-Cycle DP Instructions<br>Four-Cycle Instructions<br>INTDP Instruction                     | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-17<br>4-18<br>4-20<br>4-22<br>4-24<br>4-25<br>4-26                         |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8                   | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions<br>16 × 16-Bit Multiply Instructions<br>Store Instructions<br>Load Instructions<br>Branch Instructions<br>Two-Cycle DP Instructions<br>Four-Cycle Instructions                                                  | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-17<br>4-18<br>4-20<br>4-22<br>4-22<br>4-25<br>4-26<br>4-27                 |

|        | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Pipeline<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9 | e Operation Overview<br>Fetch<br>Decode<br>Execute<br>Pipeline Operation Summary<br>e Execution of Instruction Types<br>Single-Cycle Instructions<br>16 × 16-Bit Multiply Instructions<br>Store Instructions<br>Load Instructions<br>Branch Instructions<br>Two-Cycle DP Instructions<br>Four-Cycle Instructions<br>INTDP Instructions<br>DP Compare Instructions | 4-2<br>4-3<br>4-5<br>4-6<br>4-12<br>4-16<br>4-17<br>4-18<br>4-20<br>4-22<br>4-22<br>4-24<br>4-25<br>4-26<br>4-27<br>4-28 |

4

|   |        | 4.2.12    | MPYID Instruction                                                       |

|---|--------|-----------|-------------------------------------------------------------------------|

|   |        | 4.2.13    | MPYDP Instruction                                                       |

|   |        | 4.2.14    | MPYSPDP Instruction                                                     |

|   |        | 4.2.15    | MPYSP2DP Instruction                                                    |

|   | 4.3    | Functio   | nal Unit Constraints                                                    |

|   |        | 4.3.1     | .S-Unit Constraints                                                     |

|   |        | 4.3.2     | .M-Unit Constraints 4-40                                                |

|   |        | 4.3.3     | .L-Unit Constraints                                                     |

|   |        | 4.3.4     | .D-Unit Instruction Constraints 4-52                                    |

|   | 4.4    | Perform   | nance Considerations 4-56                                               |

|   |        | 4.4.1     | Pipeline Operation With Multiple Execute Packets in a Fetch Packet 4-56 |

|   |        | 4.4.2     | Multicycle NOPs 4-58                                                    |

|   |        | 4.4.3     | Memory Considerations 4-60                                              |

| 5 | Interr | upts      |                                                                         |

|   | Desci  | ribes the | TMS320C67x DSP interrupts, including reset and nonmaskable interrupts   |

|   | (NMI)  | , and ex  | plains interrupt control, detection, and processing.                    |

|   | 5.1    | Overvie   | ew                                                                      |

|   |        | 5.1.1     | Types of Interrupts and Signals Used 5-2                                |

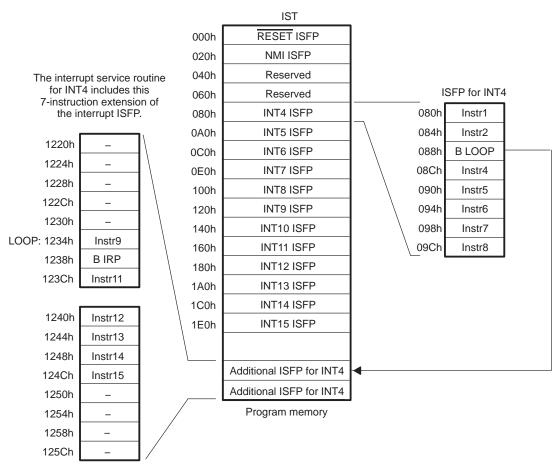

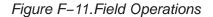

|   |        | 5.1.2     | Interrupt Service Table (IST) 5-6                                       |

|   |        | 5.1.3     | Summary of Interrupt Control Registers 5-10                             |

|   | 5.2    | Globall   | y Enabling and Disabling Interrupts 5-11                                |

|   | 5.3    | Individu  | ual Interrupt Control                                                   |

|   |        | 5.3.1     | Enabling and Disabling Interrupts 5-13                                  |

|   |        | 5.3.2     | Status of Interrupts 5-14                                               |

|   |        | 5.3.3     | Setting and Clearing Interrupts 5-14                                    |

|   |        | 5.3.4     | Returning From Interrupt Servicing 5-15                                 |

|   | 5.4    | Interrup  | ot Detection and Processing 5-16                                        |

|   |        | 5.4.1     | Setting the Nonreset Interrupt Flag 5-16                                |

|   |        | 5.4.2     | Conditions for Processing a Nonreset Interrupt 5-16                     |

|   |        | 5.4.3     | Actions Taken During Nonreset Interrupt Processing 5-18                 |

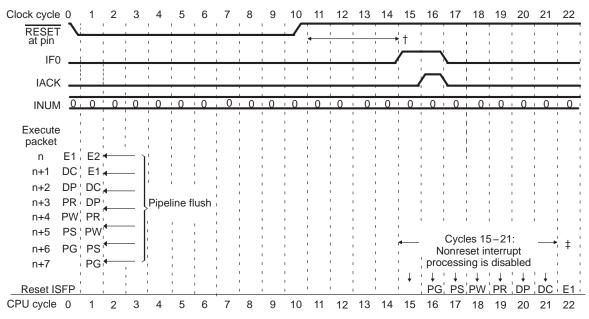

|   |        | 5.4.4     | Setting the RESET Interrupt Flag 5-19                                   |

|   |        | 5.4.5     | Actions Taken During RESET Interrupt Processing                         |

|   | 5.5    |           | nance Considerations 5-21                                               |

|   |        | 5.5.1     | General Performance                                                     |

|   |        | 5.5.2     | Pipeline Interaction                                                    |

|   | 5.6    | -         | mming Considerations                                                    |

|   |        | 5.6.1     | Single Assignment Programming                                           |

|   |        | 5.6.2     | Nested Interrupts                                                       |

|   |        | 5.6.3     | Manual Interrupt Processing 5-25                                        |

|   |        | 5.6.4     | Traps                                                                   |

| Α | Instruction Compatibility                                                                                                                                            |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| в | Mapping Between Instruction and Functional Unit         B-1           Lists the instructions that execute on each functional unit.         B-1                       |

| С | <b>.D Unit Instructions and Opcode Maps</b>                                                                                                                          |

|   | C.1Instructions Executing in the .D Functional UnitC-2C.2Opcode Map Symbols and MeaningsC-3C.332-Bit Opcode MapsC-5                                                  |

| D | <b>.L Unit Instructions and Opcode Maps</b>                                                                                                                          |

|   | D.1Instructions Executing in the .L Functional UnitD-2D.2Opcode Map Symbols and MeaningsD-3D.332-Bit Opcode MapsD-4                                                  |

| Е | .M Unit Instructions and Opcode Maps E-1<br>Lists the instructions that execute in the .M functional unit and illustrates the opcode maps for<br>these instructions. |

|   | E.1Instructions Executing in the .M Functional UnitE-2E.2Opcode Map Symbols and MeaningsE-3E.332-Bit Opcode MapsE-4                                                  |

| F | <b>.S Unit Instructions and Opcode Maps</b>                                                                                                                          |

|   | F.1Instructions Executing in the .S Functional UnitF-2F.2Opcode Map Symbols and MeaningsF-3F.332-Bit Opcode MapsF-4                                                  |

| G | <b>No Unit Specified Instructions and Opcode Maps</b>                                                                                                                |

|   | G.1Instructions Executing With No Unit SpecifiedG-2G.2Opcode Map Symbols and MeaningsG-2G.332-Bit Opcode MapsG-3                                                     |

| н | Revision HistoryH-1Lists the changes made since the previous version of this document.                                                                               |

# Figures

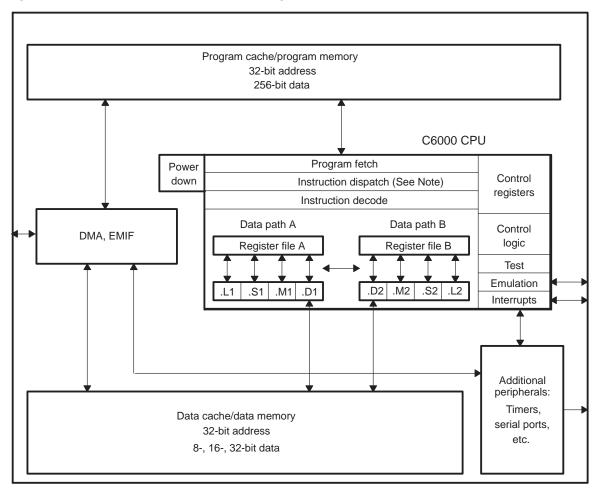

| 1–1  | TMS320C67x DSP Block Diagram                                           |

|------|------------------------------------------------------------------------|

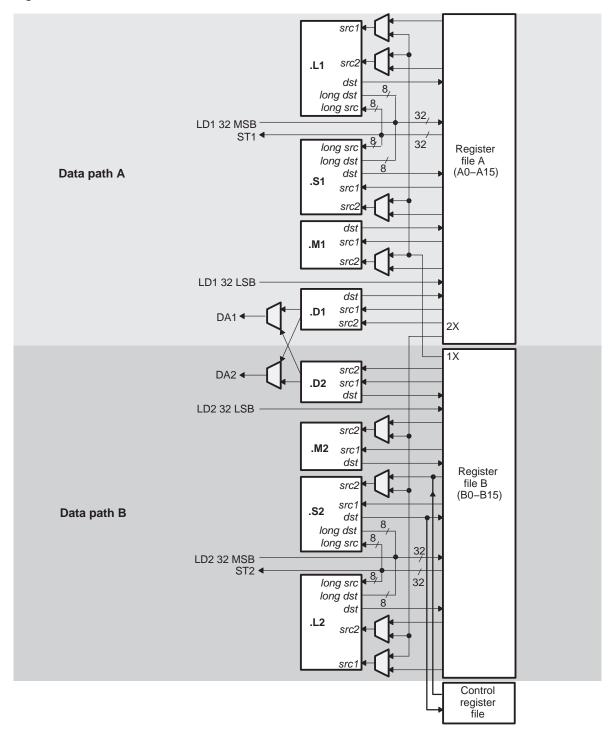

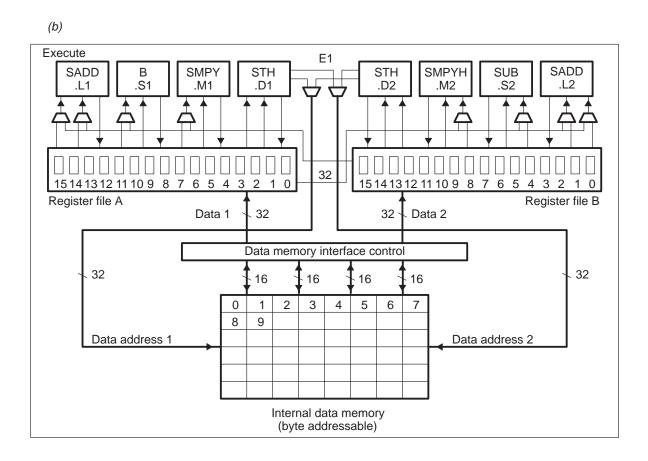

| 2–1  | TMS320C67x CPU Data Paths 2-3                                          |

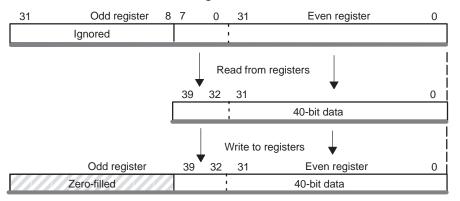

| 2–2  | Storage Scheme for 40-Bit Data in a Register Pair 2-4                  |

| 2–3  | Addressing Mode Register (AMR) 2-10                                    |

| 2–4  | Control Status Register (CSR) 2-13                                     |

| 2–5  | PWRD Field of Control Status Register (CSR) 2-13                       |

| 2–6  | Interrupt Clear Register (ICR) 2-16                                    |

| 2–7  | Interrupt Enable Register (IER) 2-17                                   |

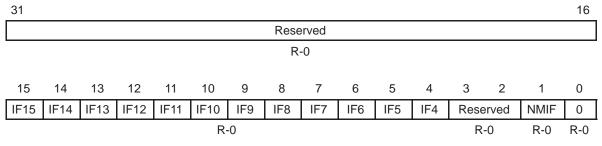

| 2–8  | Interrupt Flag Register (IFR) 2-18                                     |

| 2–9  | Interrupt Return Pointer Register (IRP) 2-19                           |

| 2–10 | Interrupt Set Register (ISR) 2-20                                      |

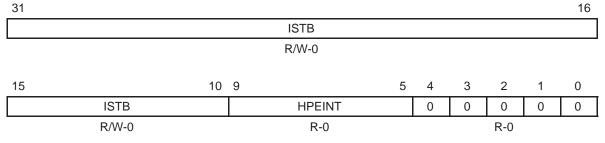

| 2–11 | Interrupt Service Table Pointer Register (ISTP) 2-21                   |

| 2–12 | NMI Return Pointer Register (NRP) 2-22                                 |

| 2–13 | E1 Phase Program Counter (PCE1) 2-22                                   |

| 2–14 | Floating-Point Adder Configuration Register (FADCR) 2-24               |

| 2–15 | Floating-Point Auxiliary Configuration Register (FAUCR) 2-27           |

| 2–16 | Floating-Point Multiplier Configuration Register (FMCR) 2-31           |

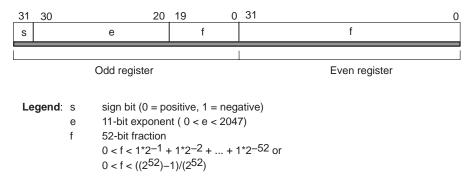

| 3–1  | Single-Precision Floating-Point Fields 3-11                            |

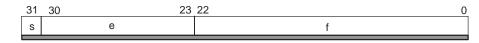

| 3–2  | Double-Precision Floating-Point Fields                                 |

| 3–3  | Basic Format of a Fetch Packet 3-15                                    |

| 3–4  | Examples of the Detectability of Write Conflicts by the Assembler 3-24 |

| 4–1  | Pipeline Stages 4-2                                                    |

| 4–2  | Fetch Phases of the Pipeline 4-3                                       |

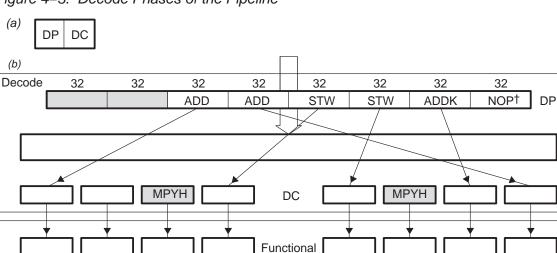

| 4–3  | Decode Phases of the Pipeline 4-4                                      |

| 4–4  | Execute Phases of the Pipeline 4-5                                     |

| 4–5  | Pipeline Phases                                                        |

| 4–6  | Pipeline Operation: One Execute Packet per Fetch Packet 4-6            |

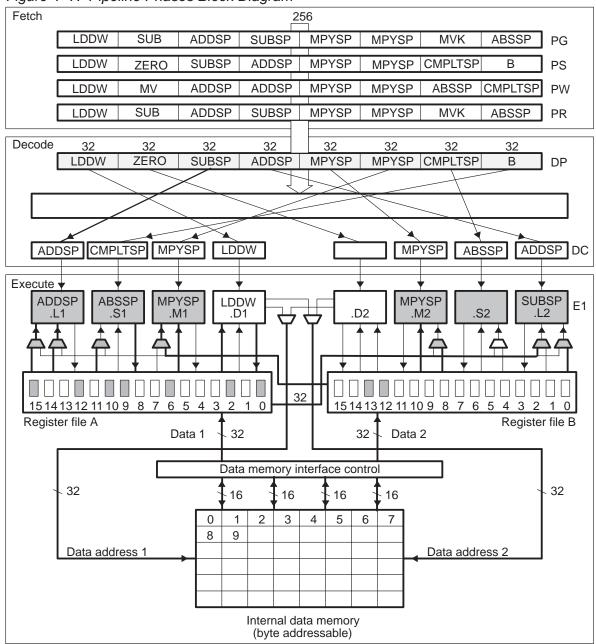

| 4–7  | Pipeline Phases Block Diagram 4-10                                     |

| 4–8  | Single-Cycle Instruction Phases 4-16                                   |

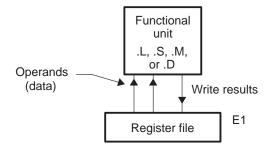

| 4–9  | Single-Cycle Instruction Execution Block Diagram 4-16                  |

| 4–10 | Multiply Instruction Phases 4-17                                       |

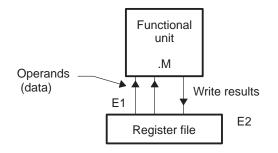

| 4–11 | Multiply Instruction Execution Block Diagram 4-17                      |

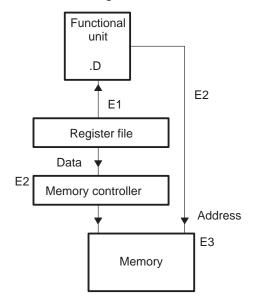

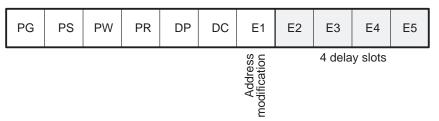

| 4–12 | Store Instruction Phases 4-18                                          |

| 4–13 | Store Instruction Execution Block Diagram 4-19                         |

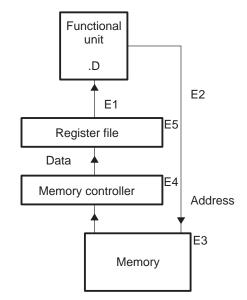

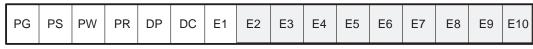

| 4–14 | Load Instruction Phases 4-20                                           |

| 4–15 | Load Instruction Execution Block Diagram 4-21                          |

| 4–16 | Branch Instruction Phases 4-22                                         |

| 4–17 | Branch Instruction Execution Block Diagram 4-23                        |

| 4–18 | Two-Cycle DP Instruction Phases                                             | 4-24 |

|------|-----------------------------------------------------------------------------|------|

| 4–19 | Four-Cycle Instruction Phases                                               |      |

| 4–20 | INTDP Instruction Phases                                                    |      |

| 4–21 | DP Compare Instruction Phases                                               |      |

| 4-22 | ADDDP/SUBDP Instruction Phases                                              |      |

| 4–23 | MPYI Instruction Phases                                                     |      |

| 4-24 | MPYID Instruction Phases                                                    |      |

| 4–25 | MPYDP Instruction Phases                                                    |      |

| 4–26 | MPYSPDP Instruction Phases                                                  |      |

| 4–27 | MPYSP2DP Instruction Phases                                                 |      |

| 4–28 | Pipeline Operation: Fetch Packets With Different Numbers of Execute Packets |      |

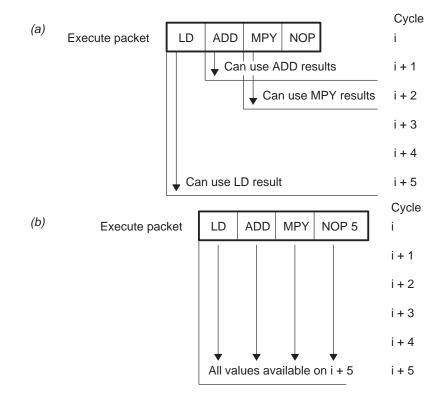

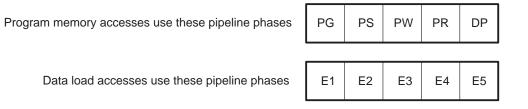

| 4–29 | Multicycle NOP in an Execute Packet                                         |      |

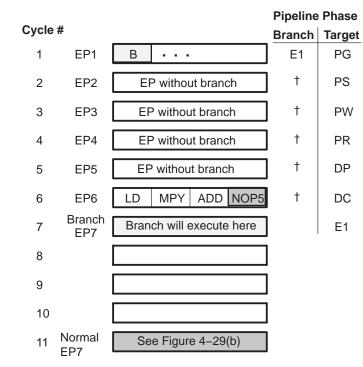

| 4–30 | Branching and Multicycle NOPs                                               |      |

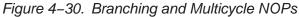

| 4–31 | Pipeline Phases Used During Memory Accesses                                 |      |

| 4–32 | Program and Data Memory Stalls                                              |      |

| 4–33 | 8-Bank Interleaved Memory                                                   |      |

| 4–34 | 8-Bank Interleaved Memory With Two Memory Spaces                            |      |

| 5–1  | Interrupt Service Table                                                     |      |

| 5–2  | Interrupt Service Fetch Packet                                              |      |

| 5–3  | Interrupt Service Table With Branch to Additional Interrupt Service Code    |      |

|      | Located Outside the IST                                                     |      |

| 5–4  | Nonreset Interrupt Detection and Processing: Pipeline Operation             |      |

| 5–5  | RESET Interrupt Detection and Processing: Pipeline Operation                |      |

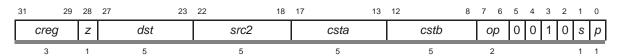

| C–1  | 1 or 2 Sources Instruction Format                                           |      |

| C-2  | Extended .D Unit 1 or 2 Sources Instruction Format                          |      |

| C-3  | Load/Store Basic Operations                                                 |      |

| C-4  | Load/Store Long-Immediate Operations                                        |      |

| D–1  | 1 or 2 Sources Instruction Format                                           |      |

| D–2  | 1 or 2 Sources, Nonconditional Instruction Format                           |      |

| D-3  | Unary Instruction Format                                                    |      |

| E–1  | Extended M-Unit with Compound Operations                                    |      |

| E–2  | Extended .M Unit 1 or 2 Sources, Nonconditional Instruction Format          |      |

| E-3  | Extended .M-Unit Unary Instruction Format                                   |      |

| F–1  | 1 or 2 Sources Instruction Format                                           |      |

| F–2  | Extended .S Unit 1 or 2 Sources Instruction Format                          |      |

| F–3  | Extended .S Unit 1 or 2 Sources, Nonconditional Instruction Format          |      |

| F–4  | Unary Instruction Format                                                    |      |

| F–5  | Extended .S Unit Branch Conditional, Immediate Instruction Format           |      |

| F–6  | Call Unconditional, Immediate with Implied NOP 5 Instruction Format         |      |

| F–7  | Branch with NOP Constant Instruction Format                                 |      |

| F–8  | Branch with NOP Register Instruction Format                                 |      |

| F–9  | Branch Instruction Format                                                   |      |

| F–10 | MVK Instruction Format                                                      |      |

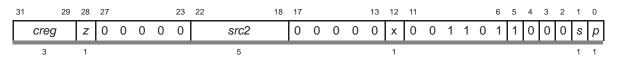

| F–11 | Field Operations                                                            |      |

| G–1  | Loop Buffer Instruction Format                                              |      |

| G–2  | NOP and IDLE Instruction Format                                             |      |

| G–3  | Emulation/Control Instruction Format                                        | G-3  |

# **Tables**

| 1–1  | Typical Applications for the TMS320 DSPs 1-3                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------|

| 2–1  | 40-Bit/64-Bit Register Pairs 2-4                                                                                               |

| 2–2  | Functional Units and Operations Performed 2-5                                                                                  |

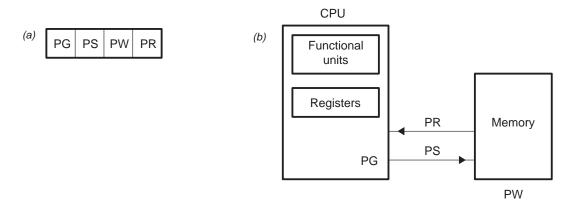

| 2–3  | Control Registers                                                                                                              |

| 2–4  | Register Addresses for Accessing the Control Registers 2-8                                                                     |

| 2–5  | Addressing Mode Register (AMR) Field Descriptions 2-10                                                                         |

| 2–6  | Block Size Calculations 2-12                                                                                                   |

| 2–7  | Control Status Register (CSR) Field Descriptions 2-14                                                                          |

| 2–8  | Interrupt Clear Register (ICR) Field Descriptions 2-16                                                                         |

| 2–9  | Interrupt Enable Register (IER) Field Descriptions 2-17                                                                        |

| 2–10 | Interrupt Flag Register (IFR) Field Descriptions 2-18                                                                          |

| 2–11 | Interrupt Set Register (ISR) Field Descriptions 2-20                                                                           |

| 2–12 | Interrupt Service Table Pointer Register (ISTP) Field Descriptions 2-21                                                        |

| 2–13 | Control Register File Extensions 2-23                                                                                          |

| 2–14 | Floating-Point Adder Configuration Register (FADCR) Field Descriptions 2-24                                                    |

| 2–15 | Floating-Point Auxiliary Configuration Register (FAUCR) Field Descriptions 2-27                                                |

| 2–16 | Floating-Point Multiplier Configuration Register (FMCR) Field Descriptions 2-31                                                |

| 3–1  | Instruction Operation and Execution Notations 3-2                                                                              |

| 3–2  | Instruction Syntax and Opcode Notations 3-7                                                                                    |

| 3–3  | IEEE Floating-Point Notations 3-10                                                                                             |

| 3–4  | Special Single-Precision Values 3-11                                                                                           |

| 3–5  | Hexadecimal and Decimal Representation for Selected Single-Precision Values 3-12                                               |

| 3–6  | Special Double-Precision Values 3-13                                                                                           |

| 3–7  | Hexadecimal and Decimal Representation for Selected Double-Precision Values 3-13                                               |

| 3–8  | Delay Slot and Functional Unit Latency                                                                                         |

| 3–9  | Registers That Can Be Tested by Conditional Operations 3-18                                                                    |

| 3–10 | Indirect Address Generation for Load/Store 3-32                                                                                |

| 3–11 | Address Generator Options for Load/Store 3-32                                                                                  |

| 3–12 | Relationships Between Operands, Operand Size, Signed/Unsigned,<br>Functional Units, and Opfields for Example Instruction (ADD) |

| 3–13 | Program Counter Values for Example Branch Using a Displacement                                                                 |

| 3–14 | Program Counter Values for Example Branch Using a Register                                                                     |

| 3–15 | Program Counter Values for B IRP Instruction                                                                                   |

| 3–16 | Program Counter Values for B NRP Instruction                                                                                   |

| 3–17 | Data Types Supported by LDB(U) Instruction                                                                                     |

| 3–18 | Data Types Supported by LDB(U) Instruction (15-Bit Offset)                                                                     |

| 3–19 | Data Types Supported by LDH(U) Instruction                   | 3-130  |

|------|--------------------------------------------------------------|--------|

| 3–20 | Data Types Supported by LDH(U) Instruction (15-Bit Offset)   |        |

| 3–21 | Register Addresses for Accessing the Control Registers       |        |

| 4–1  | Operations Occurring During Pipeline Phases                  |        |

| 4–2  | Execution Stage Length Description for Each Instruction Type |        |

| 4–3  | Single-Cycle Instruction Execution                           |        |

| 4–4  | 16 × 16-Bit Multiply Instruction Execution                   | . 4-17 |

| 4–5  | Store Instruction Execution                                  |        |

| 4–6  | Load Instruction Execution                                   | . 4-20 |

| 4–7  | Branch Instruction Execution                                 | . 4-22 |

| 4–8  | Two-Cycle DP Instruction Execution                           | . 4-24 |

| 4–9  | Four-Cycle Instruction Execution                             | . 4-25 |

| 4–10 | INTDP Instruction Execution                                  | . 4-26 |

| 4–11 | DP Compare Instruction Execution                             | . 4-27 |

| 4–12 | ADDDP/SUBDP Instruction Execution                            | . 4-28 |

| 4–13 | MPYI Instruction Execution                                   | . 4-29 |

| 4–14 | MPYID Instruction Execution                                  | . 4-30 |